ASIC/SoC & System Design¶

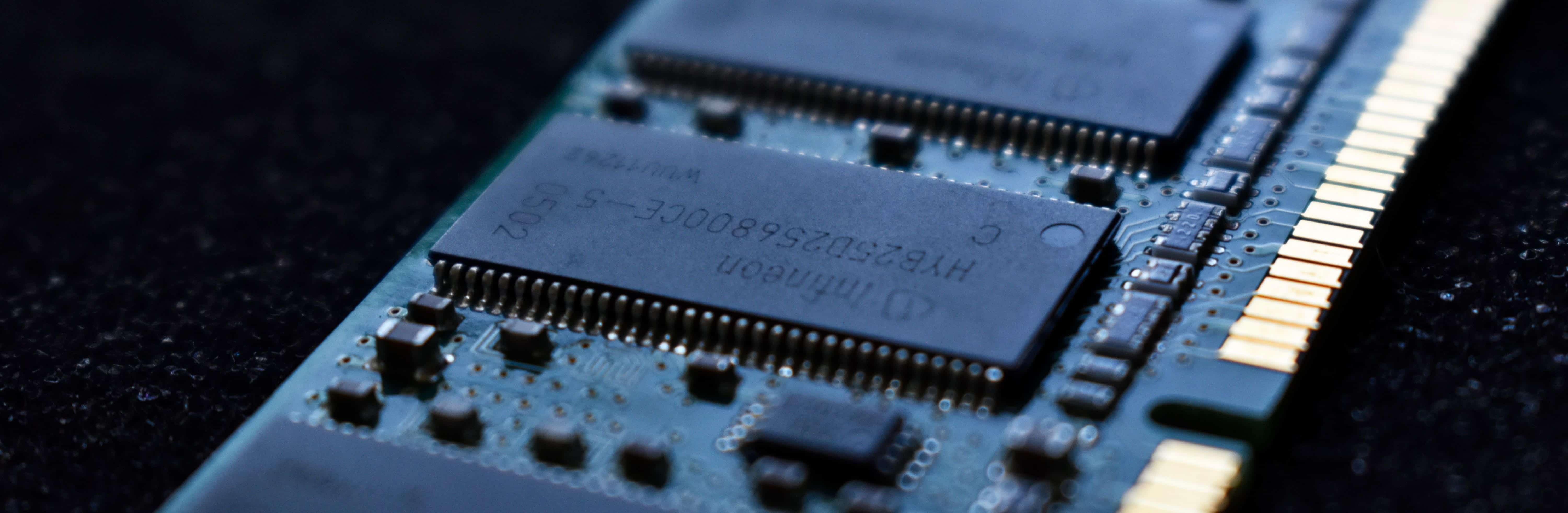

Memory¶

Understanding and working with Memory in the context of ASIC, FPGA and SoC Design can be very challenging. The specifications are complex and information is typically hard to find or proprietary.

In these articles I delve deep into what a DDR memory is made up of, how it works. We also explore memory training, calibration and timing parameters.

LPDDR5 Tutorial: Deep dive into its physical structure

Understanding LPDDR5 memory from a single memory cell to the whole memory package

DDR4 - Understanding the Basics

An in-depth look at the fundamentals of DDR Memory

DDR4 - Initialization, Training and ZQ Calibration

Understanding DRAM Initialization, ZQCL, Read/Write training, Vref Calibration and much more

DDR4 - Understanding Timing Parameters

A tutorial on DDR4 timing parameters

DDR4 - Timing Parameters Cheat Sheet

A quick reference for timing parameters

System Design¶

This collection of articles explores System Design as a whole, with an appreciation for Mechanical Design, Board Design, Power, Thermal and Cooling.

Modular Design in the Open Compute Project

A study of system design in the Open Compute Project

Facebook and the Open Compute Project

A detailed look at Facebook's server - Yosemite

HP Moonshot Dissection

Detailed study of the HP moonshot chassis